#25 - Your Chip’s First Draft: What the Netlist Really Is

"From logic gates to layout — the netlist is your design’s blueprint in the digital world."

In this issue of the “VLSI by Ankit” newsletter series, we dive into one of the most essential — yet often misunderstood — elements of the chip design process: the netlist. Whether you're debugging synthesis results or preparing for layout, the netlist is your bridge between RTL and physical reality.

📌 What Is a Netlist?

A netlist is a text-based representation of a digital circuit.

It describes:

Components (gates, flip-flops, macros, etc.)

Connections (wires or “nets”) between those components

It’s like the blueprint of your design after RTL has been synthesized.

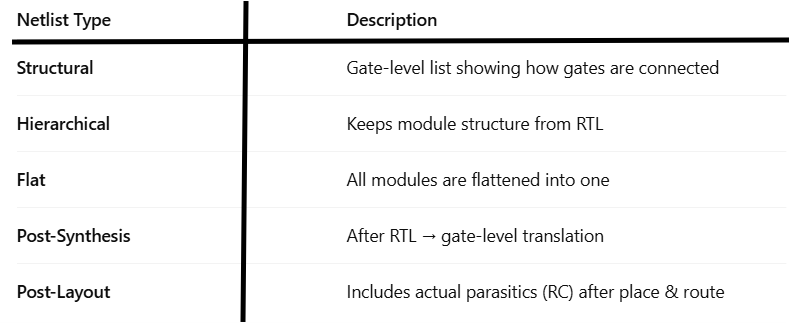

📌 Types of Netlists

There are several forms of netlists, depending on the design stage:

📌 Sample Netlist Snippet

module AND2 (input A, B, output Y);

assign Y = A & B;

endmodule

// After synthesis

AND2_X1 U1 ( .A(a), .B(b), .Y(y) );This shows an instance U1 of a 2-input AND gate connecting inputs a and b to output y.

📌 Why Is the Netlist So Important?

Debugging: You can trace signal paths and logic errors.

Place & Route: Used by physical design tools for layout.

Timing Analysis: Essential input for STA tools.

Power Estimation: Used in power analysis with real net connectivity.

DFT: ATPG tools use netlist for scan chain generation.

📌 Real-World Applications

During synthesis, your HDL code (Verilog/VHDL) gets transformed into a gate-level netlist.

During signoff, the netlist + parasitic data is used for accurate analysis.

📌 Pro Tip for Freshers

Understanding how to read a netlist will help you debug synthesis issues, timing failures, or even physical design congestion — even if you’re not a backend engineer.

“If RTL is the ‘idea,’ the netlist is the actual implementation plan.”